Lattice Semiconductor is challenging low-end products from Intel and Xilinx FPGAs, with their highest density

Lattice Semiconductor is challenging low-end products from Intel and Xilinx FPGAs, with their highest density devices having up to 100000 logic units and higher performance I/O. The Certus Pro NX series has 40000 logical units,

Time: January 13, 2023 16:16:05 Author: Click: 100

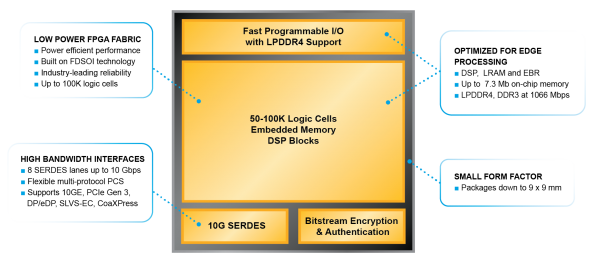

Lattice Semiconductor is challenging low-end products from Intel and Xilinx FPGAs, with their highest density devices having up to 100000 logic units and higher performance I/O.

The Certus Pro NX series has 40000 logical units and offers 10Gbit/s Ethernet and 3rd generation PCIe interfaces.

JuJu Joyce, Product Marketing Manager at Lattice Semiconductor, said: 'The starting point for Pro NX is 50000 logical units, so its goal is the next level. Pro NX will begin mass shipping in the second half of next year, after the company launched its next-generation FPGA technology Nexus5 in the first half of next year.'.

The Nexus5 FPGA will be built using the same 28 nanometer FD-SOI CMOS process technology as the current generation, which will limit the ability to increase the number of cells.

Our goal has always been to maintain price competitiveness, but we offer more value, "Joyce said. We have found that in harsh environments where many edge networks are deployed, in cellular base stations or environments without motor controlled airflow, or in small industrial camera modules, low power consumption is required to achieve simpler thermal management. He said, "Built specifically for this level of car, you can achieve higher energy efficiency

As various sensors generate more data at the edge and require higher bandwidth, their capabilities are becoming stronger and their resolutions are increasing, "he said.

I/O provides enhanced IP for low-power LPDDR4 memory interfaces and 10.3 Gbit/s for 8-channel SERDES and third-generation PCIe or 10G Ethernet connections. It also includes SLVS-EC for sensors, Coaxpress, and DisplayPort.

This series of devices also includes on-chip memory up to 7.3 megabits to support machine learning frameworks without leaving the chip.

Joyce said, "One bottleneck in artificial intelligence inference is on-chip memory, which is used to store the weights of neural networks. To overcome this bottleneck, we provide 65% on-chip memory, so for many processing functions, you don't have to rely on external memory that adds extra latency and power." "We have 18k bits of EBR embedded block RAM in the columns of the structure, and we have 512k bits of large RAM blocks located on peripheral devices connected through standard structures-

The smallest device with the lowest density interface is suitable for use in a 9 x 9 mm BGA package, with a ball pitch of 0.5mm, tightly integrated, and a rated temperature range of -40 to+125C, suitable for industrial applications.

Various artificial intelligence and machine vision stacks will be ported to new devices, and there will be an updated version of the Radiant design tool.

The SERDES analysis tool in Radiant 3.0 has been enhanced to accommodate the higher SERDES bandwidth supported by CertusPro NX devices, and signal traceability throughout the design process has been improved through a graphical user interface (GUI) to assist designers in tracking signals between HDL sources and RTL and technical views.

Radiant also allows users to choose between the Lattice Synthesis Engine (LSE) and the Synplify Pro synthesis engine. In Radiant 3.0, temporal constraints and temporal analysis are unified in both synthesis engines. Timing analysis has been separated from other operations, so it can run independently, accelerating the iterative design process by helping designers evaluate "what if" scenarios and rerun timing analysis without having to rerun mapping and layout routing.

Lattice Radiant 3.0 design software provides developers with an easy to follow user experience; the tool guides them through various steps of the development process, including design creation, importing IP, implementation, bit stream generation, downloading bit streams to FPGA, and debugging, "said Roger Do, Senior Product Line Manager for Lattice Semiconductor Software.

Developers with little or no experience working with FPGAs can quickly leverage the automation capabilities of Lattice Radiant. For experienced FPGA developers, Lattice Radiant 3.0 allows for finer grained control over FPGA settings if specific optimizations are needed, "he said.